# Capacitive 12-channel Touch Sensor

#### **Main features**

# 12-channel Capacitive Touch Sensor with Auto Sensitivity Calibration GPIO Control

- Default 4-pin GPIO Control Support (OUT1, OUT2, GPIO12, GPIO13)

- Max. 16-pin GPIO Control Support (with the not used touch channel pin)

#### **Selectable Output Operation**

- Single Key Output (Single Key Result Mode, Noise Mode)

- Multi Key Output

#### **Independently Adjustable in 8-step Sensitivity**

Adjustable Response Time and Interrupt Level by the Control Register

#### **I2C Serial Interface**

#### **IDLE Mode to Save the Power Consumption**

- Touch Wake-up: 30uA @300ms

#### **Operating Voltage**

- 2.7V ~ 5.5V

#### **Operating Conditions**

-40°C to 85°C temperature range

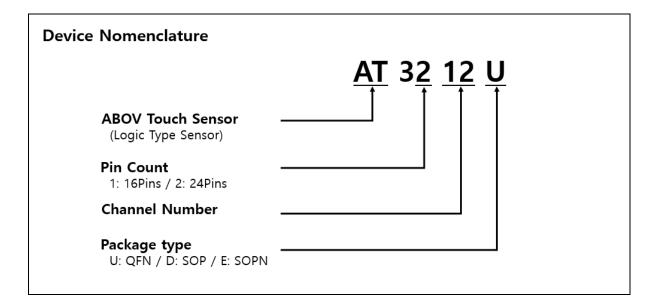

#### **Package**

- 24 QFN (AT3212U)

- 24 SOP (AT3212D)

#### **Application**

Touch Key Application

# AT3212

## **User's Manual**

V 1.2

# **Revision history**

| Version | Date       | Revision list                                                          |

|---------|------------|------------------------------------------------------------------------|

| 1.0     | 2017.02.15 | First Release                                                          |

| 1.1     | 2018.04.03 | Two registers' description is added : START_THD(0x00), STEP_THD(0x01). |

| 1.2     | 2020.01.14 | RELEASE_INT_DELAY register is added.                                   |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

|         |            |                                                                        |

# Version 1.2 Published by Sensor Solution team 2020 ABOV Semiconductor Co. Ltd. all rights reserved.

Additional information of this manual may be served by ABOV Semiconductor offices in Korea or distributors.

ABOV Semiconductor reserves the right to make changes to any information here in at any time without notice.

The information, diagrams and other data in this manual are correct and reliable;

However, ABOV Semiconductor is in no way responsible for any violations of patents or other rights of the third party generated by the use of this manual.

2

AT3212

#### 1. Overview

#### 1.1 General Feature

- 12-channel Capacitive Sensor with Auto Sensitivity Calibration

- GPIO Control

- Selectable Output Operation

- Single Key Output / Multi-Key Output Mode

- · Independently Adjustable in 8-step Sensitivity

- Adjustable Response Time and Interrupt Level by the Control Registers

- I2C Serial Interface

- IDLE Mode to Save the Power Consumption

- Touch Wake up: 30uA @ 300ms

- Operating Voltage

- 2.7V ~ 5.5V

- Operating Temperature : -40 °C ~ +85 °C

| Device name | Touch CH | Package |

|-------------|----------|---------|

| AT3212U     | 12CH     | 24 QFN  |

| AT3212D     | 12CH     | 24 SOP  |

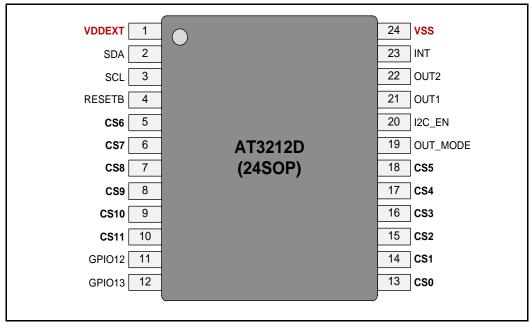

# 2. Pin Description

| Pl    | KG    | NIANAT   |                                                                      | Shared |

|-------|-------|----------|----------------------------------------------------------------------|--------|

| 24QFN | 24SOP | NAME     | Function                                                             | with   |

| 1     | 4     | RESETB   | System Reset (Low Reset)                                             | -      |

| 2     | 5     | CS6      | Capactive Sensing Channel 6                                          | GPIO6  |

| 3     | 6     | CS7      | Capactive Sensing Channel 7                                          | GPIO7  |

| 4     | 7     | CS8      | Capactive Sensing Channel 8                                          | GPIO8  |

| 5     | 8     | CS9      | Capactive Sensing Channel 9                                          | GPIO9  |

| 6     | 9     | CS10     | Capactive Sensing Channel 10                                         | GPIO10 |

| 7     | 10    | CS11     | Capactive Sensing Channel 11                                         | GPIO11 |

| 8     | 11    | GPIO12   | General Purpose Input Output Pin 12                                  | -      |

| 9     | 12    | GPIO13   | General Purpose Input Output Pin 13                                  | -      |

| 10    | 13    | CS0      | Capactive Sensing Channel 0                                          | GPIO0  |

| 11    | 14    | CS1      | Capactive Sensing Channel 1                                          | GPIO1  |

| 12    | 15    | CS2      | Capactive Sensing Channel 2                                          | GPIO2  |

| 13    | 16    | CS3      | Capactive Sensing Channel 3                                          | GPIO3  |

| 14    | 17    | CS4      | Capactive Sensing Channel 4                                          | GPIO4  |

| 15    | 18    | CS5      | Capactive Sensing Channel 5                                          | GPIO5  |

| 16    | 19    | OUT_MODE | Output Mode Selection (1 : Single Key Output / 0 : Multi Key Output) | -      |

| 17    | 20    | I2C_EN   | Wake-up Input for I2C Enable for the sleep mode                      | -      |

| 18    | 21    | OUT1     | Digital Output Pin 1                                                 | -      |

| 19    | 22    | OUT2     | Digital Output Pin 2                                                 | -      |

| 20    | 23    | INT      | Interrupt Output (Open-drain)                                        | -      |

| 21    | 24    | VSS      | Supply Ground                                                        | -      |

| 22    | 1     | VDDEXT   | Power (2.7V to 5.5V)                                                 |        |

| 23    | 2     | SDA      | I2C Data (Open-drain)                                                | -      |

| 24    | 3     | SCL      | I2C Clock (Open-drain)                                               | -      |

#### 3. Pin Assignment

Figure 1 24-QFN Pin Assignment

Figure 2 24-SOP Pin Assignment

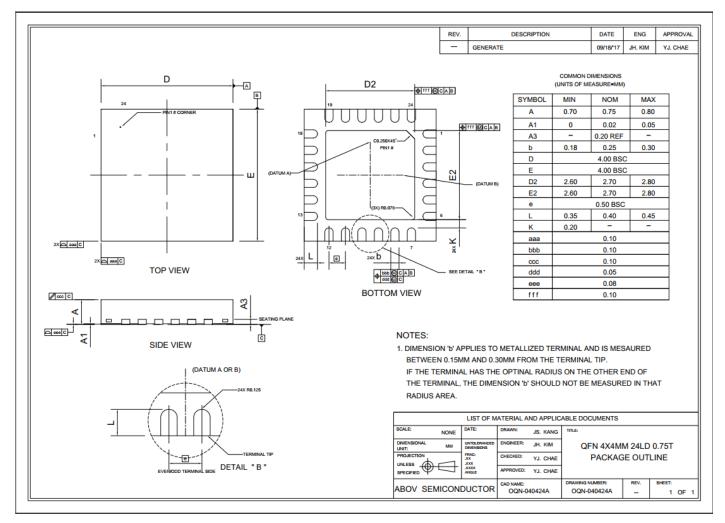

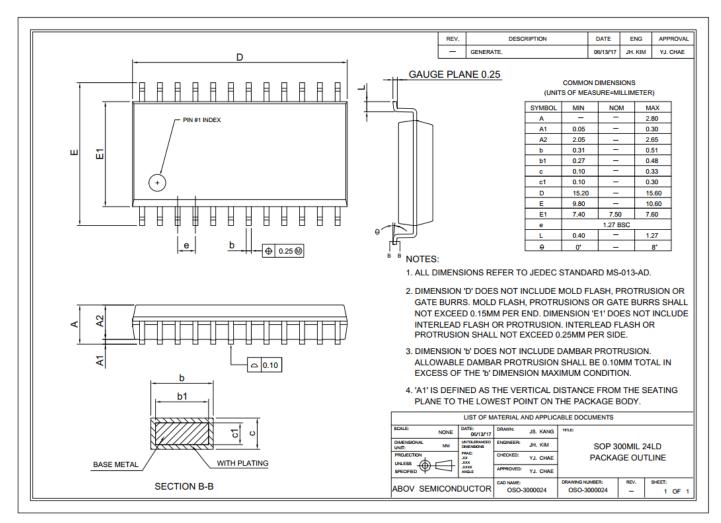

#### 4. Package Diagram

Figure 3 24-pin QFN Package

6 AT3212

Figure 4 24-pin SOP Package

7

#### 5. Electrical Characteristics

#### 5.1 Absolute Maximum Ratings

**Table 5-1 Absolute Maximum Ratings**

| Parameter               | Symbol | Rating       | Unit       |

|-------------------------|--------|--------------|------------|

| Cumbi. Valtaga          | VDD    | -0.3~+6.5    | V          |

| Supply Voltage          | VSS    | -0.3~+0.3    | V          |

|                         | VI     | -0.3~VDD+0.3 | V          |

|                         | VO     | -0.3~VDD+0.3 | V          |

| Normal Valtage Die      | IOH    | 10           | mA         |

| Normal Voltage Pin      | ΣΙΟΗ   | 80           | mA         |

|                         | IOL    | 20           | mA         |

|                         | ΣIOL   | 160          | mA         |

| Total Power Dissipation | PT     | 600          | mW         |

| Storage Temperature     | TSTG   | -65 ~ +150   | $^{\circ}$ |

Note) Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### 5.2 ESD Characteristics

**Table 5-2 ESD Characteristics**

| Mode  | Polarity    | Max.   | Reference |

|-------|-------------|--------|-----------|

|       |             | 2,000V | VDD       |

| H.B.M | Pos. / Neg. | 2,000V | VSS       |

|       |             | 2,000V | P to P    |

|       |             | 200V   | VDD       |

| M.M   | Pos. / Neg. | 200V   | VSS       |

|       |             | 200V   | P to P    |

| CDM   | Pos. / Neg. | 1,000V | DIDECT    |

| C.D.M |             | 1,000V | DIRECT    |

#### 5.3 Latch-up Characteristics

**Table 5-3 Latch-up Characteristics**

| Mode                      | Polarity | Max.  | Test Step |

|---------------------------|----------|-------|-----------|

| Current                   | Positive | 200mA | 25mA      |

| (I – Mode)                | Negative | 200mA | 25mA      |

| VDD-VSS<br>(Over Voltage) | Positive | 8.25V | -         |

### **5.4 Recommended Operating Conditions**

**Table 5-4 Recommended Operation Conditions**

| Parameter             | Symbol | Condition               | MIN | TYP | MAX | Unit |

|-----------------------|--------|-------------------------|-----|-----|-----|------|

| Supply Voltage        | VDD    | Touch Sensing Operation | 2.7 | -   | 5.5 | ٧    |

| Operating Temperature | TOPR   | VDD=2.7~5.5V            | -40 | -   | 85  | °C   |

#### 5.5 Power-On-Reset Characteristics

**Table 5-5 Recommended Operation Conditions**

| Parameter             | Symbol | Condition | MIN  | TYP | MAX | Unit |

|-----------------------|--------|-----------|------|-----|-----|------|

| Operating Voltage     |        |           | VSS  | -   | 5.5 | V    |

| Operating Temperature |        |           | -40  | -   | +85 | °C   |

| VDD Rise Rate         | VRR    |           | 0.05 | -   | 50  | V/ms |

#### 6. I<sup>2</sup>C Interface

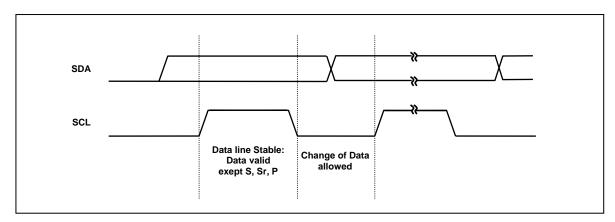

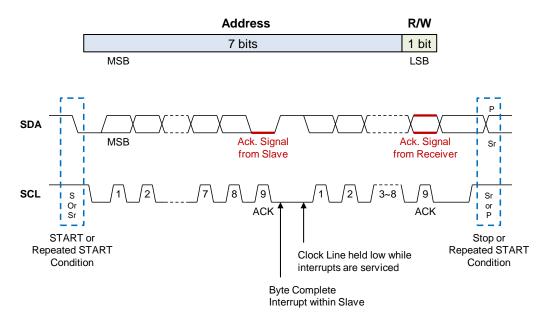

#### 6.1 I<sup>2</sup>C Bit Transfer (Data Validity)

The data on the SDA line must be stable during HIGH period of the clock, SCL. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. The exceptions are START(S), repeated START(Sr) and STOP(P) condition where data line changes when clock line is high.

Figure 5 Bit Transfer on the I<sup>2</sup>C-Bus

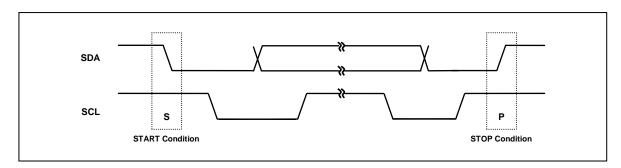

#### 6.2 Start / Repeated Start / Stop

One master can issue a START (S) condition to notice other devices connected to the SCL, SDA lines that it will use the bus. A STOP (P) condition is generated by the master to release the bus lines so that other devices can use it.

A high to low transition on the SDA line while SCL is high defines a START (S) condition.

A low to high transition on the SDA line while SCL is high defines a STOP (P) condition.

START and STOP conditions are always generated by the master. The bus is considered to be busy after START condition. The bus is considered to be free again after STOP condition, ie, the bus is busy between START and STOP condition. If a repeated START condition (Sr) is generated instead of STOP condition, the bus stays busy. So, the START and repeated START conditions are functionally identical.

Figure 6 START and STOP Condition

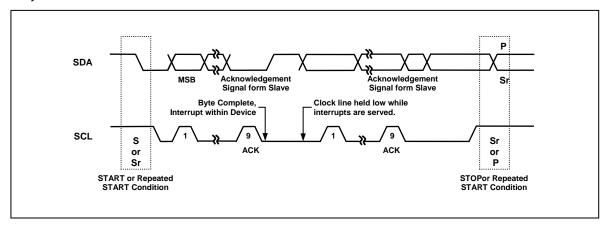

#### 6.3 Data Transfer

Every byte put on the SDA line must be 8-bits long. The number of bytes that can be transmitted per transfer is unlimited. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first. If a slave can't receive or transmit another complete byte of data until it has performed some other function, it can

hold the clock line SCL LOW to force the master into a wait state. Data transfer then continues when the slave is ready for another byte of data and releases clock line SCL.

Figure 7 Data Transfer on the I<sup>2</sup>C-Bus

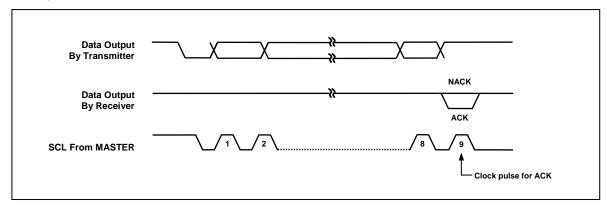

#### 6.4 Acknowledge

The acknowledge related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse. When a slave is addressed by a master (Address Packet), and if it is unable to receive or transmit because it's performing some real time function, the data line must be left HIGH by the slave. And also, when a slave addressed by a master is unable to receive more data bits, the slave receiver must release the SDA line (Data Packet). The master can then generate either a STOP condition to abort the transfer, or a repeated START condition to start a new transfer.

Figure 8 Acknowledge on the I<sup>2</sup>C-Bus

If a master receiver is involved in a transfer, it must signal the end of data to the slave transmitter by not generating an acknowledge on the last byte that was clocked out of the slave. The slave transmitter must release the data line to allow the master to generate a STOP or repeated START condition.

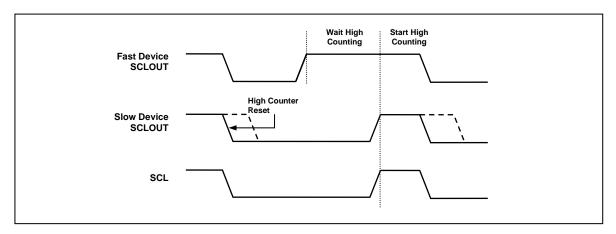

#### 6.5 Synchronization / Arbitration

Clock synchronization is performed using the wired-AND connection of I<sup>2</sup>C interfaces to the SCL line. This means that a HIGH to LOW transition on the SCL line will cause the devices concerned to start counting off their LOW period and it will hold the SCL line in that state until the clock HIGH state is reached. However the LOW to HIGH transition of this clock may not change the state of the SCL line if another clock is still within its LOW period. In this way, a synchronized

11

SCL clock is generated with its LOW period determined by the device with the longest clock LOW period, and its HIGH period determined by the one with the shortest clock HIGH period.

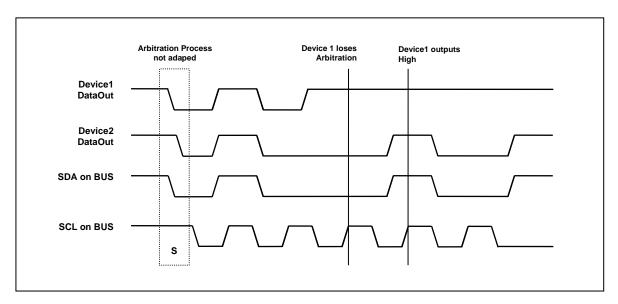

A master may start a transfer only if the bus is free. Two or more masters may generate a START condition. Arbitration takes place on the SDA line, while the SCL line is at the HIGH level, in such a way that the master which transmits a HIGH level, while another master is transmitting a LOW level will switch off its DATA output state because the level on the bus doesn't correspond to its own level. Arbitration continues for many bits until a winning master gets the ownership of I<sup>2</sup>C bus. Its first stage is comparison of the address bits.

Figure 9 Clock Synchronization during Arbitration Procedure

Figure 10 Arbitration Procedure of Two Masters

12

#### 6.6 First Byte

#### 6.6.1 Slave Address

The slave address of the AT3212 Chip is 0xF0 (F0h).

#### 6.6.2 R/W (Read or Write)

The direction of data, read or write, is decided by the 1-bit value behind of the address 7-bit data.

Figure 11 First Byte (Slave Address and R/W)

#### 6.7 I<sup>2</sup>C Write and Read Operations

The figures as below represents the I2C write and read operation

Write the register 0x02 to 0x03 with 2-byte data 0x33 and 0x22.

| START | ART Device Address ACK |     | Register Address | ACK | Write Data | ACK | Write Data | ACK | STOP |

|-------|------------------------|-----|------------------|-----|------------|-----|------------|-----|------|

| START | 0xF0                   | ACK | 0x02             | ACK | 0x33       | ACK | 0x22       | ACK | 3101 |

Read the register 0x02 to 0x03.

| ISTARTI | Address ACK | Register Address<br>0x02 | ACK | STOP |

|---------|-------------|--------------------------|-----|------|

|---------|-------------|--------------------------|-----|------|

| START | Device Address<br>0xF1 | ACK | Read Data<br>0x33 | ACK | Read Data<br>0x22 | ACK | STOP |

|-------|------------------------|-----|-------------------|-----|-------------------|-----|------|

|-------|------------------------|-----|-------------------|-----|-------------------|-----|------|

From Master to Slave

From Slave to Master

# 7. Register List

# 7.1 I2C Register Map

| Register              | Addr. | Register Function and Description |                |           |          |                  |                  |           |          |  |

|-----------------------|-------|-----------------------------------|----------------|-----------|----------|------------------|------------------|-----------|----------|--|

| Name                  | (HEX) | Bit7                              | Bit6           | Bit5      | Bit4     | Bit3             | Bit2             | Bit1      | Bit0     |  |

| START_THD             | 00h   |                                   | START_THD[7:0] |           |          |                  |                  |           |          |  |

| STEP_THD              | 01h   |                                   |                |           | STEP_1   | ΓHD[7:0]         |                  |           |          |  |

| SENSITIVITY1          | 02h   | Reserved                          |                | Ch1[2:0]  |          | Reserved         |                  | Ch0[2:0]  |          |  |

| SENSITIVITY2          | 03h   | Reserved                          |                | Ch3[2:0]  |          | Reserved         |                  | Ch2[2:0]  |          |  |

| SENSITIVITY3          | 04h   | Reserved                          |                | Ch5[2:0]  |          | Reserved         |                  | Ch4[2:0]  |          |  |

| SENSITIVITY4          | 05h   | Reserved                          |                | Ch7[2:0]  |          | Reserved         |                  | Ch6[2:0]  |          |  |

| SENSITIVITY5          | 06h   | Reserved                          |                | Ch9[2:0]  |          | Reserved         |                  | Ch8[2:0]  |          |  |

| SENSITIVITY6          | 07h   | Reserved                          |                | Ch11[2:0] |          | Reserved         |                  | Ch10[2:0] |          |  |

| CTRL1                 | 08h   | MS                                | Reserved       | Reserved  | Reserved | Reserved         | Reserved         | Reserved  | Reserved |  |

| CTRL2                 | 09h   | Reserved                          | Reserved       | Reserved  | Reserved | SRST             | SLEEP            | Reserved  | Reserved |  |

| REF_RST1              | 0Ah   | Ch7                               | Ch6            | Ch5       | Ch4      | Ch3              | Ch2              | Ch1       | Ch0      |  |

| REF_RST2              | 0Bh   | Reserved                          | Reserved       | Reserved  | Reserved | Ch11             | Ch10             | Ch9       | Ch8      |  |

| CH_HOLD1              | 0Ch   | Ch7                               | Ch6            | Ch5       | Ch4      | Ch3              | Ch2              | Ch1       | Ch0      |  |

| CH_HOLD2              | 0Dh   | Reserved                          | Reserved       | Reserved  | Reserved | Ch11             | Ch10             | Ch9       | Ch8      |  |

| OUTPUT1               | 10h   | OUT                               | 3[1:0]         | OUT       | 2[1:0]   | OUT <sup>-</sup> | 1[1:0]           | OUT       | 0[1:0]   |  |

| OUTPUT2               | 11h   | OUT                               | 7[1:0]         | OUT       | 6[1:0]   | OUT              | 5[1:0] OUT4[1:0] |           | 4[1:0]   |  |

| OUTPUT3               | 12h   | OUT1                              | 1[1:0]         | OUT1      | 0[1:0]   | OUT              | OUT9[1:0]        |           | 3[1:0]   |  |

| GPIO_CTRL1            | 13h   | Ch7                               | Ch6            | Ch5       | Ch4      | Ch3              | Ch2              | Ch1       | Ch0      |  |

| GPIO_CTRL2            | 14h   | OUT2                              | OUT1           | GPIO13    | GPIO12   | Ch11             | Ch10             | Ch9       | Ch8      |  |

| STATE_CHECK           | 15h   |                                   |                |           | STATE_C  | HECK[7:0]        |                  |           |          |  |

| PMOD                  | 1Dh   | Reserved                          | Reserved       | Reserved  | Reserved | Reserved         |                  | PMOD[2:0] |          |  |

| HOLD_TIME             | 1Eh   |                                   |                |           | HOLD_T   | IME[7:0]         |                  |           |          |  |

| OPTION_FUNC           | 1Fh   | Reserved                          | Reserved       | Reserved  | MKN      | FASTT            | MKEY             | RHOLD     | KHOLD    |  |

| HW_SUM_CNT            | 20h   |                                   |                |           | HW_SUM   | _CNT[7:0]        |                  |           |          |  |

| STOP_DELAY            | 23h   |                                   |                |           | STOP_DI  | ELAY[7:0]        |                  |           |          |  |

| STOP_WAKEL            | 24h   |                                   |                |           | STOP_W   | AKEL[7:0]        |                  |           |          |  |

| STOP_WAKECL           | 25h   |                                   |                |           | STOP_WA  | AKECL[7:0]       |                  |           |          |  |

| CHATTER_NUM           | 26h   |                                   |                |           | CHATTER  | _NUM[7:0]        |                  |           |          |  |

| RELEASE_INT_<br>DELAY | 27h   |                                   |                | RE        | LEASE_IN | T_DELAY[         | 7:0]             |           |          |  |

| SAVE_FS               | 2Ah   |                                   |                |           | SAVE_    | FS[7:0]          |                  |           |          |  |

| RECAL                 | FEh   | Reserved                          | Reserved       | Reserved  | Reserved | Reserved         | Reserved         | Reserved  | RECAL    |  |

|                       |       |                                   |                |           |          |                  |                  |           |          |  |

15

#### 7.2 Register Description

#### 7.2.1 Senitivity Control Register

**START\_THD** (Start Threshold Control Register)

Address: 00h Type: R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5 | Bit4   | Bit3     | Bit2 | Bit1 | Bit0 |

|---------------|-------|------|------|------|--------|----------|------|------|------|

| START_THD     | 00h   |      |      |      | START_ | THD[7:0] |      |      |      |

#### **Description**

The default(initial) value for this register is 0x14 (Decimal number 20). User can set the start value of threshold.

| Bit Name           | Default | Function                                                   |

|--------------------|---------|------------------------------------------------------------|

| START_THD<br>[7:0] | 0x14    | 0x00 : 0 0x01 : 1 0x13 : 19 0x14 : 20 (Default) 0xFF : 255 |

**STEP\_THD** (Step Threshold Control Register)

Address: 01h Type: R/W

| Register Name | Addr. | Bit7          | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------------|-------|---------------|------|------|------|------|------|------|------|

| STEP_THD      | 01h   | STEP_THD[7:0] |      |      |      |      |      |      |      |

#### **Description**

The default(initial) value for this register is 0x14 (Decimal number 20). User can set the step value of threshold. The real threshold level value is calculated as <u>'start value(20) + step value(20) \* sensitivity register's setting.'</u>

| Bit Name          | Default | Function                                              |

|-------------------|---------|-------------------------------------------------------|

| STEP_THD<br>[7:0] | 0x14    | 0x00: 0 0x01: 1 0x13: 19 0x14: 20 (Default) 0xFF: 255 |

SENSITIVIY1 (Channel 0 and 1 Sensitivity Control 1 Register)

Address: 02h Type: R/W

| Register Name | Addr. | Bit7     | Bit6 | Bit5     | Bit4 | Bit3     | Bit2 | Bit1     | Bit0 |

|---------------|-------|----------|------|----------|------|----------|------|----------|------|

| SENSITIVITY1  | 02h   | Reserved |      | Ch1[2:0] |      | Reserved |      | Ch0[2:0] |      |

#### **Description**

The default(initial) value for this register is 0x33. The sensitivy of channel 0 and 1 are adjustable by the register SENSITIVY1. User can adjust the sensitivity with Chx[2:0] values.

The real threshold (initial setting) is 80 from 'start value(20) + step value(20) \* sensitivity level (3).' If START\_THD = 0x64 (100), STEP\_THD = 0x0A (10), SENSITIVITY = 0x05 (5), the calculated threshold is 150 from 100 + (10 \* 5).

When user modifies the value of START\_THD or STEP\_THD register, please change the sensitivity register value again. Because the touch sensor reloads the value of START\_THD and STEP\_THD registers after the sensitivity register's value is changed.

| Bit Name  | Default | Function                                                                                |                                                   |  |  |  |  |

|-----------|---------|-----------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|

| Chx0[2:0] | 011     | Sensitivity Level Selection 000 : High (Thick Cover) 001 : 010 : 011 : Normal (Default) | 100 :<br>101 :<br>110 :<br>111 : Low (Thin cover) |  |  |  |  |

SENSITIVIY2 (Channel 2 and 3 Sensitivity Control 2 Register)

Address : 03h Type : R/W

| Register Name | Addr. | Bit7     | Bit6     | Bit5 | Bit4 | Bit3     | Bit2 | Bit1     | Bit0 |

|---------------|-------|----------|----------|------|------|----------|------|----------|------|

| SENSITIVITY2  | 03h   | Reserved | Ch3[2:0] |      |      | Reserved |      | Ch2[2:0] | •    |

#### **Description**

The default(initial) value for this register is 0x33. The sensitivy of channel 2 and 3 are adjustable by the register SENSITIVY2. User can adjust the sensitivity with Chx[2:0] values.

| Bit Name  | Default | Function                                                                                |                                                   |  |  |  |  |

|-----------|---------|-----------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|

| Chx0[2:0] | 011     | Sensitivity Level Selection 000 : High (Thick Cover) 001 : 010 : 011 : Normal (Default) | 100 :<br>101 :<br>110 :<br>111 : Low (Thin cover) |  |  |  |  |

**SENSITIVIY3** (Channel 4 and 5 Sensitivity Control 3 Register)

Address: 04h Type: R/W

| Register Name | Addr. | Bit7     | Bit6     | Bit5 | Bit4 | Bit3     | Bit2 | Bit1     | Bit0 |

|---------------|-------|----------|----------|------|------|----------|------|----------|------|

| SENSITIVITY3  | 04h   | Reserved | Ch5[2:0] |      |      | Reserved |      | Ch4[2:0] |      |

#### Description

The default(initial) value for this register is 0x33. The sensitivy of channel 4 and 5 are adjustable by the register SENSITIVY3. User can adjust the sensitivity with Chx[2:0] values.

| Bit Name  | Default | Function                                                                                |                                                   |  |  |  |  |

|-----------|---------|-----------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|

| Chx0[2:0] | 011     | Sensitivity Level Selection 000 : High (Thick Cover) 001 : 010 : 011 : Normal (Default) | 100 :<br>101 :<br>110 :<br>111 : Low (Thin cover) |  |  |  |  |

**SENSITIVIY4** (Channel 6 and 7 Sensitivity Control 4 Register)

Address: 05h Type: R/W

| Register Name | Addr. | Bit7     | Bit6 | Bit5     | Bit4 | Bit3     | Bit2 | Bit1     | Bit0 |

|---------------|-------|----------|------|----------|------|----------|------|----------|------|

| SENSITIVITY4  | 05h   | Reserved |      | Ch7[2:0] |      | Reserved |      | Ch6[2:0] |      |

#### **Description**

The default(initial) value for this register is 0x33. The sensitivy of channel 6 and 7 are adjustable by the register SENSITIVY4. User can adjust the sensitivity with Chx[2:0] values.

| Bit Name  | Default | Function                                                |                                 |  |  |  |  |

|-----------|---------|---------------------------------------------------------|---------------------------------|--|--|--|--|

|           |         | Sensitivity Level Selection<br>000 : High (Thick Cover) | 100 :                           |  |  |  |  |

| Chx0[2:0] | 011     | 001 :                                                   | 101 :                           |  |  |  |  |

|           |         | 010 :<br>011 : Normal (Default)                         | 110 :<br>111 : Low (Thin cover) |  |  |  |  |

**SENSITIVIY5** (Channel 8 and 9 Sensitivity Control 5 Register)

Address: 06h Type: R/W

| Register Name | Addr. | Bit7     | Bit6 | Bit5     | Bit4 | Bit3     | Bit2 | Bit1     | Bit0 |

|---------------|-------|----------|------|----------|------|----------|------|----------|------|

| SENSITIVITY5  | 06h   | Reserved |      | Ch9[2:0] |      | Reserved |      | Ch8[2:0] |      |

#### **Description**

The default(initial) value for this register is 0x33. The sensitivy of channel 8 and 9 are adjustable by the register SENSITIVY5. User can adjust the sensitivity with Chx[2:0] values.

| Bit Name  | Default | Function                                                                                |                                                   |  |  |  |  |  |

|-----------|---------|-----------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|--|

| Chx0[2:0] | 011     | Sensitivity Level Selection 000 : High (Thick Cover) 001 : 010 : 011 : Normal (Default) | 100 :<br>101 :<br>110 :<br>111 : Low (Thin cover) |  |  |  |  |  |

SENSITIVIY6 (Channel 10 and 11 Sensitivity Control 6 Register)

Address: 07h Type: R/W

| Register Name | Addr. | Bit7     | Bit6 | Bit5      | Bit4 | Bit3     | Bit2 | Bit1      | Bit0 |

|---------------|-------|----------|------|-----------|------|----------|------|-----------|------|

| SENSITIVITY6  | 07h   | Reserved |      | Ch11[2:0] |      | Reserved |      | Ch10[2:0] |      |

#### **Description**

The default(initial) value for this register is 0x33. The sensitivy of channel 10 and 11 are adjustable by the register SENSITIVY6. User can adjust the sensitivity with Chx[2:0] values.

| Bit Name  | Default | Function                                                |                        |  |  |  |  |  |

|-----------|---------|---------------------------------------------------------|------------------------|--|--|--|--|--|

|           |         | Sensitivity Level Selection<br>000 : High (Thick Cover) | 100 :                  |  |  |  |  |  |

| Chx0[2:0] | 011     | 001 :                                                   | 101 :                  |  |  |  |  |  |

|           |         | 010 :                                                   | 110:                   |  |  |  |  |  |

|           |         | 011 : Normal (Default)                                  | 111 : Low (Thin cover) |  |  |  |  |  |

#### 7.2.2 General Control Register

CTRL1 (General Control 1 Register)

Address: 08h Type: R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5 | Bit4 | Bit3     | Bit2 | Bit1 | Bit0 |

|---------------|-------|------|------|------|------|----------|------|------|------|

| CTRL1         | 08h   | MS   |      |      |      | Reserved |      |      |      |

#### **Description**

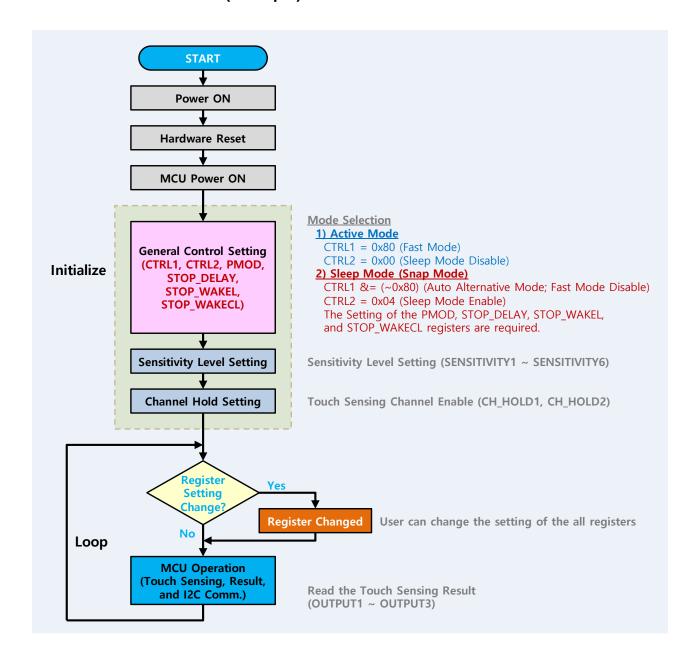

The default(initial) value for this register is 0x80. If the MS bit is clear and the sleep mode is enabled (SLEEP bit at CTRL2), the sensing function can be operated with SLEEP mode (SNAP). If the MS bit is set, the sensing function will be operated alone without SLEEP mode.

| Bit Name | Default                                   | Function      |  |  |  |  |  |

|----------|-------------------------------------------|---------------|--|--|--|--|--|

|          | Mode Selection                            |               |  |  |  |  |  |

| MS       | 80h 0 : Auto alternative (fast/slow) mode |               |  |  |  |  |  |

|          |                                           | 1 : Fast mode |  |  |  |  |  |

CTRL2 (General Control 2 Register)

Address: 09h Type: R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5  | Bit4 | Bit3 | Bit2  | Bit1 | Bit0  |

|---------------|-------|------|------|-------|------|------|-------|------|-------|

| CTRL2         | 09h   |      | Rese | erved |      | SRST | SLEEP | Rese | erved |

#### **Description**

The default(initial) value for this register is 0x00. All the digitial part and I2C part except of the analog part are reset when SRST bit is set. If he sleep mode is enabled, SLEEP bit is set, the current consumption can be getting very low. But the report time (response) time will be more longer than normal operation (Sleep mode disable).

| Bit Name | Default | Function                                                              |  |  |  |

|----------|---------|-----------------------------------------------------------------------|--|--|--|

| SRST     | 0       | Software Reset  0 : Software Reset Disable  1 : Software Reset Enable |  |  |  |

| SLEEP    | 0       | Sleep Mode Enable 0 : Sleep Mode Disable 1 : Sleep Mode Enable        |  |  |  |

#### 7.2.3 Channel Reference Reset Control Register

**REF\_RST1** (Channel Reference Reset Control 1 Register)

Address: 0Ah Type: R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------------|-------|------|------|------|------|------|------|------|------|

| REF_RST1      | 0Ah   | Ch7  | Ch6  | Ch5  | Ch4  | Ch3  | Ch2  | Ch1  | Ch0  |

#### Description

The default(initial) value for this register is 0x00. The reference value of each channel will be renewing when chx is set.

| Bit Name | Default | Function                    |  |  |  |  |

|----------|---------|-----------------------------|--|--|--|--|

| Chx      | Chx 0   | 0 : Reference Reset Disable |  |  |  |  |

| CIIX     |         | 1 : Reference Reset Enable  |  |  |  |  |

REF\_RST2 (Channel Reference Reset Control 2 Register)

Address : 0Bh Type : R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5  | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------------|-------|------|------|-------|------|------|------|------|------|

| REF_RST2      | 0Bh   |      | Rese | erved |      | Ch11 | Ch10 | Ch9  | Ch8  |

#### Description

The default(initial) value for this register is 0x00. The reference value of each channel will be renewing when chx is set.

| Bit Name | Default | Function                    |

|----------|---------|-----------------------------|

| Chy      | Chx 0   | 0 : Reference Reset Disable |

| Clix     |         | 1 : Reference Reset Enable  |

#### 7.2.4 Channel Sensing Hold Control Register

CH\_HOLD1 (Hold Control 1 Register for Channel 0 ~ 7)

Address : 0Ch Type : R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------------|-------|------|------|------|------|------|------|------|------|

| CH_HOLD1      | 0Ch   | Ch7  | Ch6  | Ch5  | Ch4  | Ch3  | Ch2  | Ch1  | Ch0  |

#### **Description**

The default(initial) value for this register is 0x00. The operation of each channel is indepently available to control. When Chx bit is set, the operation of the sensing will be hold.

| Bit Name | Default | Function                                                       |

|----------|---------|----------------------------------------------------------------|

| Chx      | 0       | 0 : Operation Enable (Sensing) 1 : Operation Hold (No Sensing) |

CH\_HOLD2 (Hold Control 2 Register for Channel 8 ~ 11)

Address : 0Dh Type : R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5  | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------------|-------|------|------|-------|------|------|------|------|------|

| CH_HOLD2      | 0Bh   |      | Rese | erved |      | Ch11 | Ch10 | Ch9  | Ch8  |

#### **Description**

The default(initial) value for this register is 0x00. The operation of each channel is indepently available to control. When Chx bit is set, the operation of the sensing will be hold.

22

| Bit Name | Default | Function                        |  |  |  |  |

|----------|---------|---------------------------------|--|--|--|--|

| Chy      | 0       | 0 : Operation Enable (Sensing)  |  |  |  |  |

| Clix     | Chx 0   | 1 : Operation Hold (No Sensing) |  |  |  |  |

#### 7.2.5 Channel Sensing Hold Control Register

**OUTPUT1** (Output Data 1 Register for Channel 0 ~ 3)

Address: 10h

Type: R (Read Only)

| Register Name | Addr. | Bit7 | Bit6   | Bit5 | Bit4   | Bit3 | Bit2   | Bit1 | Bit0   |

|---------------|-------|------|--------|------|--------|------|--------|------|--------|

| OUTPUT1       | 10h   | OUT  | 3[1:0] | OUT  | 2[1:0] | OUT  | 1[1:0] | OUT  | 0[1:0] |

#### **Description**

The OUTx[1:0] data is the each channel's sensing result.

| Bit Name  | Default | Function                                                                                                                      |  |  |  |

|-----------|---------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| OUT3[1:0] | 00      | <ul><li>00 : No Output (Not Touched)</li><li>01 : Reserved</li><li>10 : Reserved</li><li>11 : High Output (Touched)</li></ul> |  |  |  |

| OUT2[1:0] | 00      | 00 : No Output (Not Touched) 01 : Reserved 10 : Reserved 11 : High Output (Touched)                                           |  |  |  |

| OUT1[1:0] | 00      | 00 : No Output (Not Touched) 01 : Reserved 10 : Reserved 11 : High Output (Touched)                                           |  |  |  |

| OUT0[1:0] | 00      | 00 : No Output (Not Touched) 01 : Reserved 10 : Reserved 11 : High Output (Touched)                                           |  |  |  |

**OUTPUT2** (Output Data 1 Register for Channel 4 ~ 7)

Address: 11h

Type: R (Read Only)

| Register Name | Addr. | Bit7 | Bit6   | Bit5 | Bit4   | Bit3 | Bit2   | Bit1 | Bit0   |

|---------------|-------|------|--------|------|--------|------|--------|------|--------|

| OUTPUT2       | 11h   | OUT  | 7[1:0] | OUT  | 6[1:0] | OUT  | 5[1:0] | OUT  | 4[1:0] |

#### **Description**

The OUTx[1:0] data is the each channel's sensing result.

| Bit Name  | Default | Function                                                                            |

|-----------|---------|-------------------------------------------------------------------------------------|

| OUT3[1:0] | 00      | 00 : No Output (Not Touched) 01 : Reserved 10 : Reserved 11 : High Output (Touched) |

| OUT2[1:0] | 00      | 00 : No Output (Not Touched) 01 : Reserved 10 : Reserved 11 : High Output (Touched) |

| OUT1[1:0] | 00      | 00 : No Output (Not Touched) 01 : Reserved 10 : Reserved 11 : High Output (Touched) |

| OUT0[1:0] | 00      | 00 : No Output (Not Touched) 01 : Reserved 10 : Reserved 11 : High Output (Touched) |

**OUTPUT3** (Output Data 1 Register for Channel 8 ~ 11)

Address : 12h

Type : R (Read Only\_

| Register Name | Addr. | Bit7 | Bit6   | Bit5 | Bit4   | Bit3 | Bit2   | Bit1 | Bit0   |

|---------------|-------|------|--------|------|--------|------|--------|------|--------|

| OUTPUT3       | 12h   | OUT1 | 1[1:0] | OUT1 | 0[1:0] | OUT  | 9[1:0] | OUT  | 8[1:0] |

#### **Description**

The OUTx[1:0] data is the each channel's sensing result.

| Bit Name   | Default | Function                                                                            |

|------------|---------|-------------------------------------------------------------------------------------|

| OUT11[1:0] | 00      | 00 : No Output (Not Touched) 01 : Reserved 10 : Reserved 11 : High Output (Touched) |

| OUT10[1:0] | 00      | 00 : No Output (Not Touched) 01 : Reserved 10 : Reserved 11 : High Output (Touched) |

| OUT9[1:0]  | 00      | 00 : No Output (Not Touched) 01 : Reserved 10 : Reserved 11 : High Output (Touched) |

| OUT8[1:0]  | 00      | 00 : No Output (Not Touched) 01 : Reserved 10 : Reserved 11 : High Output (Touched) |

#### 7.2.6 GPIO Control Register

GPIO\_CTRL1 (GPIO Control & Data 1 Register for Channel 0 ~ 7)

Address: 13h Type: R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------------|-------|------|------|------|------|------|------|------|------|

| GPIO_CTRL1    | 13h   | Ch7  | Ch6  | Ch5  | Ch4  | Ch3  | Ch2  | Ch1  | Ch0  |

#### **Description**

The default(initial) value for this register is 0x00. If the some channel is in hold mode (refer to CH\_HOLD1), this channel can output in digital output (high or low). But if the channel is in sensing mode, this channel cannot output.

| Bit Name | Default | Function                        |

|----------|---------|---------------------------------|

| Chx      | 0       | 0 : Low Level<br>1 : High Level |

GPIO\_CTRL2 (GPIO Control & Data 1 Register for Channel 8 ~ 11 and LED pins)

Address: 14h Type: R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5   | Bit4   | Bit3 | Bit2 | Bit1 | Bit0 |

|---------------|-------|------|------|--------|--------|------|------|------|------|

| GPIO_CTRL2    | 14h   | OUT2 | OUT1 | GPIO13 | GPIO12 | Ch11 | Ch10 | Ch9  | Ch8  |

#### Description

The default(initial) value for this register is 0xF0. If the some channel is in hold mode (refer to CH\_HOLD2), this channel can output in digital output (high or low). But if the channel is in sensing mode, this channel cannot output.

| Bit Name | Default | Function                        |

|----------|---------|---------------------------------|

| Chx      | 0       | 0 : Low Level<br>1 : High Level |

| GPIO12   | 1       | 0 : Low Level<br>1 : High Level |

| GPIO13   | 1       | 0 : Low Level<br>1 : High Level |

| OUT1     | 1       | 0 : Low Level<br>1 : High Level |

| OUT2     | 1       | 0 : Low Level<br>1 : High Level |

#### 7.2.7 Function Control Register

STATE\_CHECK (Chip Reset State Check Register)

Address: 15h Type: R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------------|-------|------|------|------|------|------|------|------|------|

| STATE_CHECK   | 15h   | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

#### **Description**

The default(initial) value for this register is 0x00, and user can write the arbitrary value at this register. Then user reads this value for this register. If the read value doesn't equal to 0x00, this device was restarted (or reset).

| Bit Name | Default | Function                                                                              |

|----------|---------|---------------------------------------------------------------------------------------|

| Bitx     | 0x00    | 0x00 : Initial Value after reset (Default) Arbitray value except of 0x00 : User value |

**PMOD** (IDLE Mode Duty Time Register)

Address: 1Dh Type: R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5     | Bit4 | Bit3 | Bit2 | Bit1     | Bit0 |

|---------------|-------|------|------|----------|------|------|------|----------|------|

| PMOD          | 1Dh   |      |      | Reserved | I    |      | F    | PMOD[2:0 | )]   |

#### Description

The default(initial) value for this register is 0x02. User can set the duty time of the IDLE mode with 8 steps. The device in the IDLE mode check the touch detection (once) every the duty time (ex : 300ms).

The total duty time for IDLE mode equals 100ms + (100ms \* step value).

| Bit Name  | Default | Function                                                                                                          |

|-----------|---------|-------------------------------------------------------------------------------------------------------------------|

| PMOD[2:0] | 0x02    | 0x00 : 100ms 0x01 : 200ms 0x02 : 300ms (Default) 0x03 : 400ms 0x04 : 500ms 0x05 : 600ms 0x06 : 700ms 0x07 : 800ms |

**HOLD\_TIME** (Touch Key Hold Time Register)

Address : 1Eh Type : R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5 | Bit4   | Bit3     | Bit2 | Bit1 | Bit0 |

|---------------|-------|------|------|------|--------|----------|------|------|------|

| HOLD_TIME     | 1Eh   |      |      |      | HOLD_T | IME[7:0] |      |      |      |

#### **Description**

The default(initial) value for this register is 0x0C. User can set the hold time for touch key pressed with 255 steps. If the touch key dectecting (pressed) time is greater than the hold time, the touch key is released and re-initialized. The total hold time for touch key equals (1 second \* step value).

| Bit Name           | Default | Function                                                                                                    |

|--------------------|---------|-------------------------------------------------------------------------------------------------------------|

| HLOD_TIME<br>[7:0] | 0x0C    | 0x00 : 0s 0x01 : 1s 0x02 : 2s 0x0B : 11s 0x0C : 12s (Default) 0x0D : 13s 0x0E : 14s 0xFE : 254s 0xFF : 255s |

#### **OPTION\_FUNC** (Function Option Selection Register)

Address : 1Fh Type : R/W

| Register Name | Addr. | Bit7 | Bit6     | Bit5 | Bit4 | Bit3  | Bit2 | Bit1  | Bit0  |

|---------------|-------|------|----------|------|------|-------|------|-------|-------|

| OPTION_FUNC   | 1Fh   |      | Reserved |      |      | FASTT | MKEY | RHOLD | KHOLD |

#### Description

The default(initial) value for this register is 0x09. User can set the hold time enable for touched state or reverse touched state. And user can set the multi-key mode, fast baseline tracking, and multi-key noise mode.

| Bit Name | Default | Function                                                                                                                                                                                                                                                                                                                               |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KHOLD    | 1       | Hold Time Enable Bit for Touched State  0: Disable  1: Enable (Default)  Refer to the description of the HOLD_TIME Register.  If this bit is 1 (Default) and the hold time for touched state is greater than the user hold time(HOLD_TIME register), the touch key is released and re-initialized.                                     |

| RHOLD    | 0       | Hold Time Enable Bit for Reverse Touched State  0: Disable (Default)  1: Enable  We recommend that this option is set to 0 (Disable). If this bit is 1 (Enable) and the reversed touched time by the external noise is more than 200ms (fixed reverse hold time), the touch key is released and reinitialized.                         |

| MKEY     | 0       | Multi-Key Mode Bit 0 : Single-key Mode (Default) 1 : Multi-key Mode                                                                                                                                                                                                                                                                    |

| FASTT    | 1       | Fast Baseline Tracking Option Bit 0: 1 second 1: 200ms (Default)                                                                                                                                                                                                                                                                       |

| MKN      | 0       | Multi Key Noise Bit  0 : Single Key Result Mode (Default)  Return Single Key Result from the Multi-key (Default)  1 : Noise Mode  Not Touched State (They're considered as the noise)  If the multi-key state is occurred in single key mode, the result will be single key from these multi-key or not touched with this bit setting. |

**HW\_SUM\_CNT** (Haredware Sum Count Register)

Address : 20h Type : R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5 | Bit4    | Bit3     | Bit2 | Bit1 | Bit0 |

|---------------|-------|------|------|------|---------|----------|------|------|------|

| HW_SUM_CNT    | 20h   |      |      | F    | I/W_SUM | _CNT[7:0 | )]   |      |      |

#### **Description**

The default(initial) value for this register is 0x02 (2 times). To increase the DIFF (Difference or Delta) value, user can user can set the hardware sum count. But because the sensing time is slower, the response time will be slower too and the power (current) consumption will be more increased.

| Bit Name            | Default | Function                            |

|---------------------|---------|-------------------------------------|

| HW_SUM_CNT<br>[7:0] | 0x02    | Accumulated Count for Touch Sensing |

STOP\_DELAY (IDLE Mode Start Delay Time Register)

Address : 23h Type : R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5 | Bit4    | Bit3      | Bit2 | Bit1 | Bit0 |

|---------------|-------|------|------|------|---------|-----------|------|------|------|

| STOP_DELAY    | 23h   |      |      | ;    | STOP_DE | ELAY[7:0] |      |      |      |

#### Description

The default(initial) value for this register is 0x03. User can set the delay time for starting the IDLE Mode. When the device starts the entrance to the IDLE mode in the ACTIVE mode, After the delay time was passed, the device will be in the IDLE mode.

The total delay time for starting the IDLE mode equals (500ms + 500ms \* step value).

| Bit Name            | Default | Function                                                                                      |

|---------------------|---------|-----------------------------------------------------------------------------------------------|

| STOP_DELAY<br>[7:0] | 0x03    | 0x00: 0.5s 0x01: 1s 0x02: 1.5s 0x03: 2s (Default) 0x04: 2.5s 0x05: 3s 0xFE: 127.5s 0xFF: 128s |

STOP\_WAKEL (IDLE Mode Wakeup Level Control Register)

Address: 24h Type: R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5 | Bit4   | Bit3     | Bit2 | Bit1 | Bit0 |

|---------------|-------|------|------|------|--------|----------|------|------|------|

| STOP_WAKEL    | 24h   |      |      | 5    | STOP_W | AKEL[7:0 | ]    |      |      |

#### **Description**

The default(initial) value for this register is 0x0A. User can set the wakeup level for the IDLE mode. The recommend value is 100% of threshold as the default value.

First, the device checks which the touch difference value is greater than the wakeup check level (ex: 50% from STOP\_WAKECL) twice times in a row. If the check level detection event is occurred, then the device checks that the touch difference value is greater that the wakeup level (ex: 100% from STOP\_WAKEL). If the level detection is occurred, the device will be wakeup from IDLE mode.

The total wakeup level for the IDLE mode equals (10% of the threshold \* step value).

| Bit Name            | Default | Function                                                             |

|---------------------|---------|----------------------------------------------------------------------|

| STOP_WAKEL<br>[7:0] | 0x0A    | 0x00:0% 0x01:10% 0x09:90% 0x0A:100% (Default) 0x0B:110% 0xFF:2,550%s |

STOP\_WAKECL (IDLE Mode Wakeup Check Level Control Register)

Address : 25h Type : R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5 | Bit4   | Bit3     | Bit2 | Bit1 | Bit0 |

|---------------|-------|------|------|------|--------|----------|------|------|------|

| STOP_WAKECL   | 25h   |      |      | S    | TOP_WA | KECL[7:0 | 0]   |      |      |

#### **Description**

The default(initial) value for this register is 0x05. User can set the wakeup check level for the IDLE mode. The recommend value is 50% of threshold as the default value. In more detail information, please refer to the STOP\_WALEL register.

The total wakeup check level for the IDLE mode equals (10% of the threshold \* step value).

| Bit Name             | Default | Function                                                            |

|----------------------|---------|---------------------------------------------------------------------|

| STOP_WAKECL<br>[7:0] | 0x05    | 0x00 : 0% 0x01 : 10% 0x05 : 50% (Default) 0x06 : 60% 0xFF : 2,550%s |

#### **CHATTER\_NUM** (Chattering Number Register)

Address : 26h Type : R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5 | Bit4   | Bit3     | Bit2 | Bit1 | Bit0 |

|---------------|-------|------|------|------|--------|----------|------|------|------|

| CHATTER_NUM   | 26h   |      |      | 5    | STOP_W | AKEL[7:0 | ]    |      |      |

#### Description

The default(initial) value for this register is 0x02. User can set the chattering number for the touch key state. The recommend value is 2 times (0x02). The same key has to detect more than the chattering number in a row.

| Bit Name             | Default | Function                                                                           |

|----------------------|---------|------------------------------------------------------------------------------------|

| CHATTER_NUM<br>[7:0] | 0x02    | 0x00 : None 0x01 : 1 Time 0x02 : 2 Times (Default) 0x03 : 3 Times 0xFF : 255 Times |

32 AT3212

RELEASE\_INT\_DELAY (Release Interrupt Delay Time Register)

Address: 27h Type: R/W

| Register Name         | Addr. | Bit7 | Bit6 | Bit5 | Bit4    | Bit3    | Bit2   | Bit1 | Bit0 |

|-----------------------|-------|------|------|------|---------|---------|--------|------|------|

| RELEASE_INT_<br>DELAY | 27h   |      |      | REL  | EASE_IN | T_DELA\ | /[7:0] |      |      |

#### **Description**

The default(initial) value for this register is 0x14. User can set the delay time for interrupt output at release event. When the release event is occurred, the interrupt output pin will be low pulse after delay time (default : 20ms). The total delay time for interrupt output at release event equals (1ms \* step value; Max. 255ms).

Note: This register setting data can not be saved by SAVE\_FS register. It means that host should always send the setting of this register each power on or reset.

| Bit Name                       | Default | Function                                                                                     |

|--------------------------------|---------|----------------------------------------------------------------------------------------------|

| RELEASE_INT<br>_DELAY<br>[7:0] | 0x14    | 0x00 : 0ms 0x01 : 1ms 0x02 : 2ms 0x14 : 20ms (Default) 0x15 : 21ms 0xFE : 254ms 0xFF : 255ms |

**SAVE\_FS** (Save at FLASH Memory Control Register)

Address : 2Ah Type : R/W

| Register Name | Addr. | Bit7 | Bit6 | Bit5 | Bit4  | Bit3    | Bit2 | Bit1 | Bit0 |

|---------------|-------|------|------|------|-------|---------|------|------|------|

| SAVE_FS       | 2Ah   |      |      |      | SAVE_ | FS[7:0] |      |      |      |

#### **Description**

The default(initial) value for this register is 0x00. When user write the value 0xAA to the SAVE\_FS register, the current setting for touch sensing is written to the FLASH memory. If the device is reset by hardware, the device will read the setting at the FLASH memory.

| Bit Name         | Default | Function                                                                                                                           |

|------------------|---------|------------------------------------------------------------------------------------------------------------------------------------|

| SAVE_FS<br>[7:0] | 0x00    | 0x00 : None (Default) 0xAA : Save to the Current Touch Setting to the FLASH. 0x5A : Save the H/W Calibration Setting to the FLASH. |

**RECAL** (Recalibration Control Register)

Address: FEh

Type: W (Write Only)

| Register Name | Addr. | Bit7     | Bit6 | Bit5 | Bit4 | Bit3 | Bit2  | Bit1 | Bit0 |

|---------------|-------|----------|------|------|------|------|-------|------|------|

| RECAL         | FEh   | Reserved |      |      |      |      | RECAL |      |      |

#### **Description**

The default(initial) value for this register is 0x00. User can run the recalibration for the Touch Sensing.

| Bit Name | Default | Function                                                            |

|----------|---------|---------------------------------------------------------------------|

| RECAL    | 0       | 0 : None (Default) 1 : Run the Re-calibration for the Touch Sensing |

34

#### 8. Recommended Flow Chart (Example)

35 AT3212

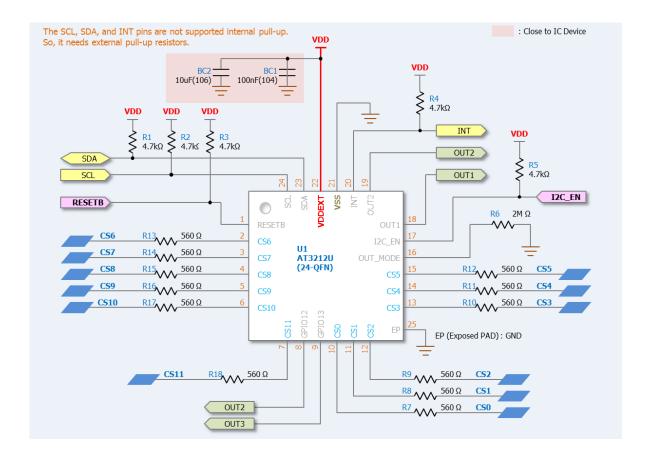

#### 9. Recommended Circuit Design

- 1) The threse three pins (SDA, SCL, and INT) are open-drain output. Then, these pins needs pull-up resistors. But if the host has already pull-up resistors, these pull-up resistors at slave don't be needed.

- 2) GPIO output pins are basically GPIO12(#8), GPIO13(#9). If the more output pins are needed, OUT1(#18) and OUT2(#19).

- 3) The OUT\_MODE pins supports the output mode selection function. In circuit, the multi key output mode is selected. (1: Single Key Output / 0: Multi Key Output)

- 4) The I2C\_EN pin should be always high with pull-up resistor. If the sleep mode is used and the wake-up is needed, the low pulse has to be input to the I2C\_EN pin.

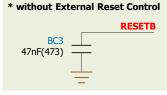

- 5) When the digital input level of the RESETB pin is low, hardware reset will be run(Active Low) . If the external reset control is not needed, please connect the capacitor (47nF) for stable operation.

36

- 6) The recommended value of channel resistor is 560 Ohms (can use 1k Ohm). In PCB layout design, channel resistor have to place besides the touch sensor device.

- 7) The bypass capacitors (Decoupling) have to place besides the touch sensor device too.

### 10. Ordering information